## EE 330 Spring 2024 HW4 Solutions

1) No of wafers produced by 248nm in 4 years= 80x24x365x4 = 2803200 cost per wafer for 248nm machine = 10M/2803200 =\$3.17 cost per process = \$35.7.

No of wafers produced by 193nm in 4 years= 20x24x365x4 = 700800 cost per wafer for 248nm machine = 40M/700800 = \$57.08

cost per process = \$570.8

wafer area =  $pi*(300*10^{-3})^2/4 = 70650 \text{ sq mm}$

die area of 90nm chip is 50 sq mm.

die/wafer for 90nm wafer = wafer area/die area = 1413 dies/ wafer

die area of 50nm chip is going to reduce by a factor of (90/50)<sup>2</sup>

This gives us the die area of the 50nm chip = 15.43 mm<sup>2</sup>

die/wafer for 50nm wafer = wafer area/die area = 4578 dies /wafer

cost per chip of a 248nm machine = 35.7/1413 = \$0.025 per chip

cost per chip of a 193nm = 570.8/4578 = \$ 0.125 per chip

Therefore, we can say that it costs about 5 times more to manufacture a chip at 50nm node.

2) Gate oxide thickness of Si-O2 = 2nm

$$\frac{\varepsilon(SiO2)*A}{d_{SiO2}} = \frac{\varepsilon(HfO2)*A}{d_{HfO2}}$$

We take the  $\varepsilon(SiO2)=3.9$  and  $\varepsilon(HfO2)=20$

We get the gate oxide thickness of HfO2 = 10.3nm

3) From lecture notes, diameter of oxide layer = 0.35nm

⇒ Volume of oxide layer =

$$\frac{4}{3}\pi \left(\frac{0.35}{2}\right)^3 = 0.0224493 \,\text{nm}^3$$

⇒ Volume of oxide layer =  $7 \,\text{nm} \times 14 \,\text{nm} \times 25 \times 10^{10} \,\text{m}$

=  $245 \,\text{nm}^3$

⇒ Number of Sticon dioxide molecules =  $\frac{245 \,\text{nm}^3}{0.0224493 \,\text{nm}^3}$

=  $10913.5 \,\text{molecules}$

4) The resistivity of Al = 2.65 \*  $10^{-8} \Omega \cdot m$

Resistance =

$$\ell \frac{L}{A}$$

=  $2 \cdot 65 \times 10^{9} \times \frac{1000 \times 10^{6}}{20 \times 10^{9} \times 40 \times 10^{9}}$

=  $33125 \Omega$

- 5) The lowest resistance material would be Silver. One of the reasons is that they are not used to form metal connects because they are more immune to oxidization as compared to Cu or Al. Also, during the metallization process, they can migrate and enter the Silicon which alters the behavior of the CMOS.

- 6) The loss of material per cut = 150um Typical thickness of 12" silicon wafer = 775um. Thickness of material removed from Silicon pull per wafer = 150um + 775um = 925um Total number of wafers from the Silicon pull = 2/925u = 2126 wafers There is an additional 0.162\*925u = 149.85um of Silicon being wasted in the process.

7)

Contact resistance → 14.6 ohms

Paly sheet → 21.7 ohms/sq.

Capacitance poly  $\rightarrow$  82 qF/ $\mu$ m<sup>2</sup> = 82 × 10<sup>-18</sup> F/ $\mu$ m<sup>2</sup>

(a)

$$1 \text{ K Hz} = \frac{1}{\text{RC}}$$

, Capacitance =  $8p \text{ F}$

Capacitor Area

8pF = Capacitance poly x Capacitor Area

$$\Rightarrow \text{ Capacitor Area} = \frac{8pF}{\text{Capacitance poly}} = \frac{8 \times 10^{-12} \text{ F}}{82 \times 10^{-18} \text{ F/um}^2}$$

⇒ Capacitance Axea = 97560.98 µm²

Resister Area

$$1000 \times 2\pi = \frac{1}{8_{\rho} F \times ((14.6 \times 2) + (21.7 \times N_{5}))}$$

If Resister length =

$$1 \text{ um}$$

Resister Width =  $916790 \text{ um}$

$$\rightarrow$$

Total Filter Aceq = 916790 um² + 97560.98 um²

= 1014350.98 um²

→ Capacitor =

$$8pF$$

Reinster =  $\frac{1}{2\pi \times 1000 \times 8p}$  =  $19.894368 M II$

$$(2\pi \times 1000) = \frac{1}{(82 \times 10^{18} \times H_{cap}) \times [(14.6 \times 2) + 21.7 \times Ns]}$$

→ 0.6 μm is minimum for 0.5 μ technology

Hus, to find minimum area, dimension of Square = (0.6 μm)<sup>2</sup>

$$\Rightarrow (2\pi \times 1000) = \frac{1}{(82 \times 10^{-18} \times A_{cap}) \times \left[ (2 \times 14.6) + (21.7 \times \frac{A_{cas}}{(0.6 \mu m)^2} \right]}$$

$$\Rightarrow 2000T = \frac{1}{(82 \times 10^{-18} \times A_{cap}) \times [(2 \times 14.6) + 21.7 \times \frac{A_{total} - A_{cap}}{0.36}]}$$

8) A) width and length dimensions are overlap of polysilicon gate and active area width =  $3\mu m$  length =  $1\mu m$

3 times higher than (b)

B) Positive photoresist = exposed material is removed when developed W is not affected by the dimensions of the Poly, only by dimensions of active but L is affected Underdeveloped photoresist = not enough is removed, Under-etched = not enough is removed. It follows if L1 is the original length (1u),

$$L=L1-2*0.1-2*0.1 = 0.6u$$

and  $W = 3u$

C) Negative photoresist = unexposed material is removed when developed As before, W is not affected by the dimensions of Poly but L is affected

Underdeveloped photoresist = too little is removed but since negative photoresist, provides too much polysilicon protection . Under-etched, not enough is removed.

Thus

$$L = L1 + 2*(0.1) - 2*(0.1) = 1u + 0.2u - 0.2u = 1u$$

and  $W = 3u$

Note in this case the two deviations compensate for each other and the desired length is obtained.

9)

(i)

$$R = \rho \frac{L}{A} = \rho \frac{L}{\text{width } \times \text{thickness}}$$

=>

$$\frac{\text{thuckness}}{25 \times 2 \times 10^6} = 1.325 \times 10^{-7} \text{ m}$$

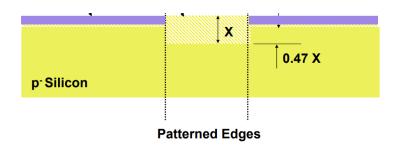

difference in wafer =

$$5000 \times 10^{10} \times (1-0.47)$$

thickness